VTMX™ - Virtual Test Mixed Signal

Imagine there is no division between the design and test worlds... and that the same design testbench can simulate the device Verilog netlist and exercise the physical chip for characterization and production!?

Conversely, imagine the test engineer can execute the test program on the tester before the silicon is available, and that all device-and-tester interactions are available pre-silicon to check out all the complex device initialization, protocols, and analog/mixed-signal set up..

Before all that become reality, introducing TSSI's VTMX!!

VTMX stands for Virtual Test with Mixed Signal. VTMX enables direct communication between the electronic design automation (EDA) world with the automated test equiopment (ATE) world.

With VTMX, test engineers can bring up their test program before silicon arrives by accessing the EDA environment directly from the ATE environment that they are familiar with, without having to know a single line of EDA language such as Verilog.

Reversely, design verification teams can interactively bringing up their design on a target ATE environment without having to know the tester's rules, restrictions, and programming language.

Features:

-

VTMX can toggle the ATE between its traditional operating mode (Physical) and the new "virtual" mode for interacting with design's netlist

-

Test engineers can get a working test program in virtual mode, and the same test program can be used in characterization and production

-

ATE test program debug mode is fully supported. Breakpoints stop the simulator the same way they do to the ATE sequencer

-

ATE microcodes are fully supported. TRIGGER, DSP send and capture, loops, conditional jumps, wait, and more are all supported

-

The ATE communicates with the EDA environment via a secure cloud or VPN connection

-

Easy configuration to connect the ATE with the EDA environment

-

Robust simulation tools and waveform analysis capabilities assist in debugging complex device functionalities

-

Design team can send protocol commands over the VTMX interface to interact with the ATE

Benefits:

-

Test engineers use the same tester environment to get a headstart on test program development while device is still in the Verilog netlist format

-

Test programs can be completed in days vs weeks/months

-

Design verification can target, or compare their test strategies on the ATE platform(s) to be used in characterization and production, and shorten the overall time to market

-

Design and test can communicate via the same VTMX tool environment and avoid lag time in "over the wall" process

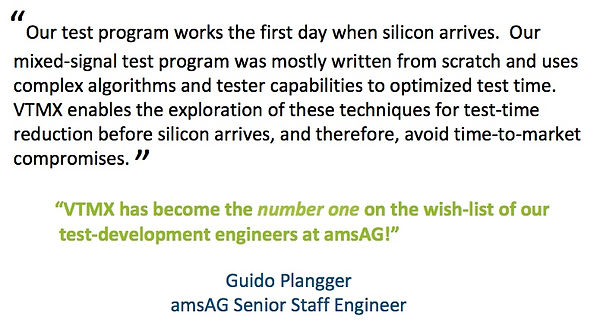

Customer Success:

-

Company: amsAG International headquarters in Austria.

-

Device: mixed-signal device with 256 sensors, 256 16-bit ADCs, 200Mbps LVDS, with SPI, and I2C protocols.

-

Status:

System Requirements:

-

Simulator: Cadence IUS or XCelium, Mentor Questa, Synopsys VCS.

-

Tester: Cohu DiamondX, or X-Series running Unison 1709 or later.

-

Workstation: Linux CentOS 6.2.