# Waveform Generation Language

2026.0

---

---

## Introduction

Waveform Generation Language (WGL), by Test Systems Strategies, Inc. (TSSI), is a data description language. It is used to convey an editable ASCII representation of the data between design and test.

For large volume of data, especially with scan data, a binary format for the ScanState and Pattern sections is supported, to be used (if desired) in place of ASCII pattern data. (Do *not* edit a WGL file that contains binary pattern data; null pattern bits may be deleted by the editor.)

WGL supports both scan hardware and test program generation that uses defined variables and embedded equation expressions.

## WGL Language Conventions

The WGL language is free-form (multiple white spaces are treated as a single white space and line returns are ignored) and limited to a line length of 512 characters. WGL reserved words are not case sensitive; keywords may be entered in any mix of upper and lower case letters. For user-defined names and pattern state characters, case is significant. The language uses the ASCII set of printable characters as legal input characters. WGL supports such features as macros, include files, in-line comments, post-compilation annotation, and many other operations normally available in programming languages.

Wherever “TDS” is mentioned, it represents a TSSI product that was introduced at the same time as the WGL creation. Stands for Test Development Series, TDS was the first application that uses the WGL standard. Hence, the state characters in WGL are often referred as TDS states, or TDSstate. TDS has gone through transformation and become the

latest TSSI product called Solstice-TDS. In this specification, TDS and Solstice-TDS will be used interchangeably.

Wherever “WDB” is mentioned, it represents a structured random access database that is a binary equivalent of WGL. WDB stands for Waveform DataBase or WGL DataBase, interchangeably. The purpose for having WDB as a tester-neutral database is to enable programmable data exchange between the design tools and the various tester environments.

TSSI pattern conversion product provides a suite of WDB database clients for test program development to all leading automatic test equipment (ATE) formats. The database clients can also re-generate Verilog testbench for design re-simulation.

A library of application programming interface (API) for the WDB is also available for end users to develop their own proprietary database clients.

## WGL Syntax Notation Conventions

In describing the syntax of WGL, the following variation of the Backus-Naur Formalism (BNF) is used:

- Two colons followed by an equivalence sign ( ::= ) denote a syntactic category to syntactic rules relationship.

- Double quotation marks ( “ ” ) or **bold** typeface denote the literal use of a reserved word, typographical symbol, or parameter. If double quotation marks are to be used literally, they are enclosed within single quotation marks ( ‘ ’ ).

- Angle brackets ( < > ) denote the use of a user-defined name, integer or floating number.

- An equivalence sign ( = ) denotes the definition of a WGL reserved word or lexical primitive.

- Brackets ( [ ] ) denote optional syntax, appearing 0 or one time.

- Braces ( { } ) denote an unspecified repetition ( 0 to  $n$  times) of the enclosed syntax. (This notation implies that the enclosed syntax is optional, since zero repetitions of a syntax is optional usage.)

- A vertical bar ( | ) denotes separate choices of syntax.

- Parentheses ( ( ) ) denote grouping of syntax options.

The use of *italics* in a text reference to a WGL syntactical element indicates higher-level BNF constructs. Such constructs are expanded to their full definition in the BNF accompanying the reference. For example, references to *FormatDecl* would appear in the appropriate BNF production as follows:

```

FormatDecl ::= <formatName> ":" "[" <TDSstate> { "," <TDSstate> } "]" ";"

```

User-defined identifiers, such as <TDSstate>, are defined in the last section: “Glossary of WGL Terminology”.

## NOTE

---

*Do not confuse the BNF use of such typographical symbols as braces ( { } ) with WGL’s use of the same symbol. BNF uses braces to show a repetition of the action enclosed within the braces, while WGL uses braces to mark database annotations.*

---

## Comments

As in other programming languages, you can add explanatory comments to a WGL program to aid functional clarity.

These comments are preceded by the pound sign ( # ), and are not included in the WDB, the binary database output when the TDS WGL In Converter tool is run.

Third party tools can decide on what to do with WGL comments.

Comments can be inserted into any part of a WGL program except WGL annotations.<sup>1</sup> (See “[Annotations](#)”) To insert a comment into a WGL program, enter a pound sign ( # ), followed by a text string. All characters on the line, starting with the pound sign and the terminating with the carriage return marking the end of the line, are included in the comment.

A complete BNF syntactical representation of the Comment feature follows.

Comment ::= “#” <any explanatory text> <end-of-line>

Example of WGL comments in a WGL program:

---

Start Example

---

```

# Signal block

signal

clk: input;      # system clock dataReady:

output; in: input;

readWrite: bidir;

data [0..31]: bidir; # 32-bit data bus

addr [0..15]: input; # 16-bit address bus

```

---

<sup>1</sup>. The binary pattern file cannot have comments, only annotations.

end

---

End Example

---

## Identifiers

An identifier is the alphanumeric name of a signal, bus, group, TimePlate, format, timing generator, pattern, subroutine, et cetera. Identifiers must begin with an alphabetic character, and may not contain white space (such as blanks, tabs, and newline characters) or any of the following delimiting characters:

|                                  |                   |

|----------------------------------|-------------------|

| # (pound sign)                   | + (plus sign)     |

| { (left brace)                   | , (comma)         |

| } (right brace)                  | : (colon)         |

| “ (left double quotation marks)  | ; (semi-colon)    |

| ” (right double quotation marks) | [ (left bracket)  |

| .. (double periods)              | ] (right bracket) |

| ( (left parenthesis)             | .                 |

| ) (right parenthesis)            | (period)          |

Identifiers must not conflict with any of the WGL reserved words. Any names that contain special characters or reserved words must be entered as a string surrounded by double quotation marks ( “ ” ).

In the WGL syntax descriptions in this chapter, identifiers are enclosed in angle brackets ( <> ).

## Numbers

Unless noted otherwise, user-defined numeric values are integers that range from zero to the maximum integer that can be represented on your system’s architecture. Any exceptions are noted in the appropriate WGL syntax description section of this chapter.

In the WGL syntax descriptions in this chapter, user-defined numeric values are enclosed in angle brackets ( <> ).

## Reserved Words

WGL reserves certain words as its linguistic set, from which data descriptions and procedural instructions can be synthesized. These reserved words can appear only in WGL statements in the correct syntax.

The following list shows the WGL reserved words:

|                  |                  |             |            |           |

|------------------|------------------|-------------|------------|-----------|

| atepin           | event            | leadingedge | procedure  | time      |

| bidir            | exprset feedback | loop        | ps         | timegen   |

| binary           | for              | macro       | radix      | timeplate |

| boolean          | force force_or_z | ms          | reference  | timeset   |

| call             | format           | mux         | register   | timing    |

| channel          | freerunningclock | ns          | repeat     | to        |

| compare          | hex              | o           | scan       | us        |

| decimal          | hexadecimal      | octal       | scancell   | vector    |

| direction        | i                | offstate    | scanchain  | wavedata  |

| dont_care        | in               | out         | scanstate  | waveform  |

| dutpin           | initial          | output      | signal     | when      |

| edge             | input            | pattern     | skip       | window    |

| end              | integer          | period      | subroutine | datacount |

| equationdefaults | last_drive       | pingroup    | symbolic   | wide      |

| equationsheet    | last_force       | pemode      | tg         |           |

Unlike conventional programming languages, WGL cannot restrict or filter the use of reserved words. If a design has a signal name (or any other application-specific name) that conflicts with any of the WGL reserved words, the signal name must be enclosed by double quotation marks ( " " ) to differentiate the signal name from the reserved word. This must be done throughout the program wherever the signal name occurs.

## Strings

Strings are any sequence of characters surrounded by double quotation marks ( " " ). Within a string, if you want to use double quotation marks, you must precede each occurrence with a back slash ( \ ). If you want to use a back slash within a string, you must precede each occurrence with a back slash. For example, the string: \design"1"\

The equivalent WGL syntax is:

```

"\\design\"1\"\\\"

```

## WGL Syntax

WGL is a block-structured language. The body of the WGL program comprises one large structure, bracketed by opening and closing statements. Within the overall structure are smaller, more specialized structures, or blocks, each bracketed by opening and closing statements. A discussion of WGL's syntactic elements follows.

# General Syntax

In its simplest form, a WGL source file requires at least one **waveform** block with the following syntax:

```

waveform <waveFormName> [WaveformParameters]

{ WaveformBlocks }

end

```

A **waveform** block is self contained with essentials blocks such as signals, timings, and patterns to be described in the *WaveformBlocks* .

## Multi-time Domain Waveform Blocks

For devices with multiple time domains (especially when the domains are asynchronous to one another), multiple **waveform** blocks can be defined in one WGL source file. Such WGL can be translated directly to a target tester that supports multi-time domain applications. Otherwise, pattern conversion tools should merge the multiple **waveform** blocks to fit a target tester that has no multi-time domain capability.

## Free-running and Asynchronous Clocks

Even though a recommended way to specify a free-running clock or asynchronous clock is in the Signals block (see [Signals](#)), a special case of multi-time domain WGL file can be made to define these clocks. It's simply an option to use Waveform Blocks as opposed to a Signals Block.

Each of the free-running clocks and asynchronous clocks should be defined in a **waveform** block of its own time domain using a special reserve word, **freerunningclock**, in the **waveform** block's *[WaveformParameters]* .

For example:

---

Start Example

```

waveform generic (generic_domain)

signal

sig1 : input;

sig2 : input;

end

timeplate tp period 10ns

sig1 := input[0ps:P, 5ns:S];

sig2 := input[0ps:P, 5ns:S];

end

```

```

pattern pat (sig1, sig2)

vector(+, tp) := [0 0];

vector(+, tp) := [0 1];

vector(+, tp) := [1 0];

vector(+, tp) := [1 1];

vector(+, tp) := [0 0];

vector(+, tp) := [0 1];

end

end

waveform async_clocks ( freerunningclock aclkl_domain )

signal

aclk : input;

end

timeplate tp_aclk period 7.5ns:

aclk := input[0ps:D, 4ns:U];

end

pattern pat_aclk (aclk)

vector(+, aclk) := [-];

end

end

```

---

End Example

---

Note that in the example above, the pattern block for the `aclk` only has to declare 1 pattern row. If the target tester has the capability to program a free-running and/or asynchronous clock then the timing defined in the timeplate is sufficient to program the clock.

Alternatively, if `aclk` is to be programmed by patterns, there should be sufficient vector statements to ensure that the clock signal continues until all waveform domains are completed. For example, the `generic` waveform domain has 6 vectors with each vector having a 10ns period and the pattern duration will be 60ns. For the `async_clocks` domain, the timeplate period is 7.5ns and thus **8 vectors** will be required for the clock to run for 60ns. In this case, the `async_clocks` waveform becomes:

```

waveform async_clocks ( freerunningclock aclkl_domain )

signal

aclk : input;

end

timeplate tp_aclk period 7.5ns:

aclk := input[0ps:D, 4ns:U];

end

pattern pat_aclk (aclk)

repeat 8 vector(+, aclk) := [-];

end

end

```

NOTE: The **freerunningclock** reserved word is optional in this case.

## Details of a Typical Single WGL Waveform Block

Valid syntax for the *WaveformBlocks* is any of sixteen program sections. These sections are referred to as WGL programming blocks or blocks. The block names are:

|                  |             |

|------------------|-------------|

| EquationDefaults | ScanChain   |

| EquationSheet    | ScanState   |

| Formats          | Signals     |

| GlobalMode       | Subroutines |

| Patterns         | Symbolics   |

| Pin Groups       | TimeGens    |

| Registers        | TimePlates  |

| ScanCells        | TimingSets  |

The block names act as block identifiers that categorize the information in each of the program blocks used. The blocks are optional and can occur in any order, subject to the restriction that all items in a block must be defined before they are used, and a pattern block must be defined before a subroutine that uses it is defined. It is possible to create an empty WDB, a WDB with only signals defined, a WDB with signals and timing defined, a WDB with only signals and patterns defined, or a WDB with all components defined (as represented by inclusion of all program blocks describing WDB objects).

A high-level BNF syntactical representation of the WGL program follows:

```

WaveformPrograms ::= { WaveformProgram }

WaveformProgram ::= "waveform" <waveFormName> [ WaveformParameters ]

{ WaveformBlocks } "end"

WaveformParameters ::= "(" [ "freerunningclock" ] <domainName> ")"

WaveformBlocks ::= ( EquationSheet | EquationDefaults | GlobalMode | Formats

| TimeGens | PinGroups | Signals |

TimingSets | Registers | TimePlates | Symbolics | Patterns |

Subroutines | ScanCells | ScanChain | ScanState )

EquationSheet ::= "equationsheet" <equationSheetName>

{ ExpressionDecl } "end"

EquationDefaults ::= "equationdefaults" DefaultsDecl "end"

GlobalMode ::= "pmode" "[" PmodeOption "] ";"

Formats ::= "format" { FormatDecl } "end"

```

TimeGens ::= “timegen” { TgDecl } “end”

PinGroups ::= “pingroup” { PinGroupDecl } “end”

Signals ::= “signal” { SignalDecl } “end”

TimingSets ::= “timeset” <tsNumber> { TgAssign } end”

Registers ::= “register” “(” PinList “)” { RegisterDecl } “end”

TimePlates ::= “timeplate” <timeplateName> TimePlate “end”

Symbolics ::= “symbolic” SignalReference [ SymDirection] Radix

SymbolicAssignment “end”

Patterns ::= “pattern” <patternName> “(” PatternParameters “)”

PatternRows “end”

Subroutines ::= “subroutine” <subroutineName> “( ”

PatternRows “end”

ScanCells ::= “scanCell” { ScanCellDecl } “end”

ScanChain ::= “scanChain” { ChainDecl } “end”

ScanState ::= “scanState” { ScanStateDecl } “end”

An example of a typical WGL program is:

---

Start Example

---

```

waveform generic

signal

CS_ENABLE : input dutpin[P1:1]

atepin[CSENAB:1];

A-BUS [15..0] : input radix

hexadecimal

dutpin[P2:2, P3:3, P4:4, P5:5, P6:6, P7:7,

P8:8, P9:9, P10:10, P11:11,

P12:12, P13:13, P14:14, P15:15, P16:16,

P17:17]

atepin[ABUS15:2, ABUS14:3, ABUS13:4, ABUS12:5, ABUS11:6,

ABUS10:7, ABUS9:8, ABUS8:9, ABUS7:10,

ABUS6:11, ABUS5:12, ABUS4:13, ABUS3:14, ABUS2:15,

ABUS1:16, ABUS0:17];

LOAD : input dutpin[P18:18]

atepin[LOAD:18];

.

.

end

```

```

timeplate Fetch period 300ns

CS_ENABLE := input[0pS:P, 30nS:S];

A-BUS := input[0pS:D, 120nS:S, 260nS:D];

LOAD := input[0pS:P, 100nS:S];

ENP := input[0pS:P, 50nS:S];

DR := input[0pS:P, 100nS:S];

RO := input[0pS:U, 70nS:S, 180nS:U];

D-BUS := output[0pS:X, 100nS:Q, 250nS:X];

DB-BUS := output[0pS:X, 100nS:Q, 250nS:X];

AD-BUS := input[0pS:P, 100nS:S]; end

timeplate R_W period 200ns

CS_ENABLE := input[0pS:P, 30nS:S];

A-BUS := input[0pS:D, 60nS:S, 190nS:D];

LOAD := input[0pS:S];

ENP := input[0pS:S];

DR := input[0pS:S];

RO := input[0pS:U, 40nS:S, 180nS:U];

D-BUS := output[0pS:X, 60nS:Q, 190nS:X];

DB-BUS := output[0pS:X, 40nS:Q, 180nS:X];

AD-BUS := input[0pS:P, 60nS:S]; end

.

.

symbolic DB-BUS input radix hexadecimal

RESET := [1ED8];

JMP := [BE43];

LDA := [062D];

end

symbolic DB-BUS output radix binary end

pattern group_ALL (CS_ENABLE,A-BUS,LOAD,ENP,DR,RO,D-BUS,DB-BUS:I,DB-BUS:O,

AD-B S:I,AD-BUS:O)

repeat 5

vector(0, 0pS, Startup) := [1 FFFF 0 0 0 1 3D66 RESET ----- AD -- ];

{ This is the COMMENT for the first row }

vector(5, 2.5uS, Fetch) := [1 ADBB 0 0 1 0 3CDA ---- 0011111000000100 BB -- ];

vector(6, 2.8uS, R_W) := [0 0C13 1 0 1 1 ADBB ---- 0010100100101101 84 -- ];

vector(7, 3uS, Write) := [0 8D18 0 1 0 0 ADBB JMP ----- -- 99 ];

{ The WRITE cycle contains "mid-cycle I/O" on the DB-Bus.}

vector(8, 3.4uS, Fetch) := [0 EF57 0 1 0 1 ADBB ---- 1100001001000100 98 -- ];

vector(9, 3.7uS, R_W) := [0 82DD 1 0 1 0 EF57 ---- 0110000001110101 7B -- ];

call sub1();

vector(16, 5.7uS, Write) := [0 8D18 0 1 0 0 ADBB JMP ----- -- 99 ];

vector(17, 6.1uS, Fetch) := [0 EF57 0 1 0 1 ADBB ---- 1100001001000100 98 -- ];

vector(18, 6.4uS, R_W) := [0 82DD 1 0 1 0 EF57 ---- 0110000001110101 7B -- ];

vector(19, 6.6uS, Write) := [0 2927 1 1 0 0 AA03 LDA ----- -- 81 ];

vector(20, 7uS, Fetch) := [0 84F5 0 1 1 1 AA03 ---- 0100000110110111 A4 -- ];

vector(21, 7.3uS, R_W) := [1 8DB4 1 0 1 1 84F5 ---- 1100001100010001 97 -- ];

call sub1();

```

```

vector(28, 9.3uS, Write) := [0 7306 1 1 0 0 84F5 00DF ----- -- 17 ];

.

.

vector(107, 33.1uS, Fetch) := [0 9DF1 1 1 0 1 140F ---- 0010100101000010 98 -- ];

{ This is the LAST vector row}

end

subroutine sub1()

vector(0, 0pS, Write) := [1 59E7 1 0 1 1 EF57 5FC9 ----- -- 65 ];

vector(1, 400nS, Fetch) := [0 E327 0 0 0 0 EF57 ---- 0111100101000100 BF -- ];

vector(2, 700nS, R_W) := [0 28E7 1 0 1 1 E327 ---- 1101001110000110 CA -- ];

vector(3, 900nS, Write) := [1 898B 1 1 0 1 E327 5F8B ----- -- A0 ];

vector(4, 1.3uS, Fetch) := [1 AA03 0 0 0 1 E327 ---- 1001111010101101 83 -- ];

vector(5, 1.6uS, R_W) := [0 1ECD 1 0 1 0 AA03 ---- 0010001101010101 23 -- ];

end

```

---

End Example

---

## Program Block Syntax

All WGL program blocks begin with one of the WGL reserved word block names, and terminate with the reserved word ‘end’. Between these two delimiting reserved words are one or more WGL statements used to define data. These WGL statements themselves are subdivided into smaller structures that address more specific operations, such as setting timing for individual signal channels.

A colon (:) is used to assign an attribute (such as force or input) to an identifier. A colon-and-equivalence (:=) is used as an assignment operator, assigning a value (such as a numeric value) to an identifier. See the previous example of a typical WGL program for these usages.

In permitted instances commas and semi-colons are used as delimiters. When several parameters occupy the same line, each entry may be delimited by a comma (,). Each separate WGL statement must be delimited by a semicolon (;). Check the BNF notation for each WGL block for details of permissible usages.

Generally speaking, the WGL blocks are of three types: generic, tester-specific, and equation-specific.

The generic blocks let you address data that are related to the test waveforms.

The tester-specific blocks allow you to specify data values (such as in TDS WDB) that are directly related to the type of tester you are targeting.

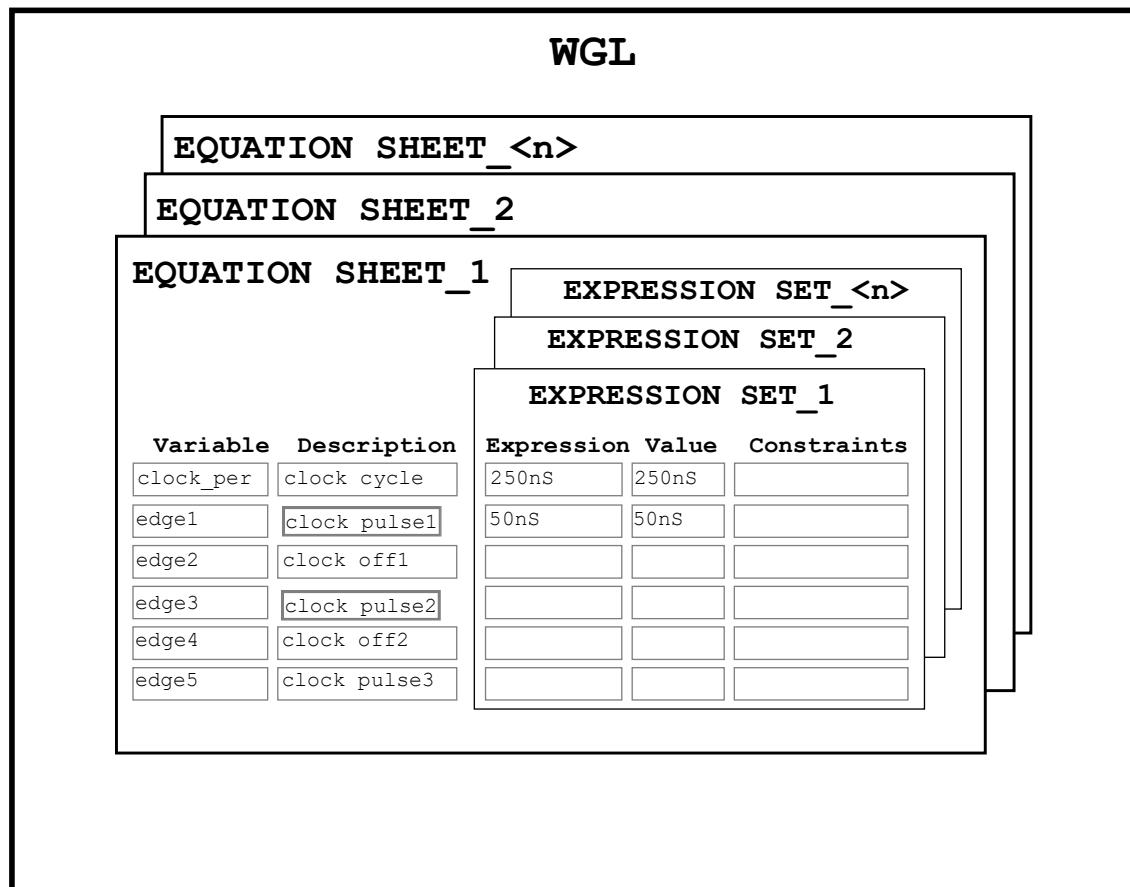

The equation-specific blocks let you assign expressions and constant values to variables that can later be used in place of time values in timing sets and TimePlates. The results of these equations are then included in the test program you can generate using a TDS WaveBridge or TesterBridge module.

While it is useful to consider the WGL blocks in these three general categories, it is important to remember that some blocks contain generic, tester-specific, and equation-specific components. For example, Signals blocks and TimePlates blocks contain both generic and tester-specific WGL statements. TimePlate blocks and TimingSet blocks contain generic, tester-specific, and equation-specific WGL statements.

Table 1 defines the block type of each of the sixteen WGL program blocks.

**Table 1. WGL program block types**

| <b>WGL Program Block</b> | <b>Type</b>                                 |

|--------------------------|---------------------------------------------|

| EquationDefaults         | equation-specific                           |

| EquationSheet            | equation-specific                           |

| Formats                  | tester-specific                             |

| GlobalMode               | generic                                     |

| Patterns                 | generic                                     |

| Pin Groups               | tester-specific                             |

| Registers                | tester-specific                             |

| Scan Cells               | generic                                     |

| Scan Chain               | generic                                     |

| Scan State               | generic                                     |

| Signals                  | generic, tester-specific                    |

| Subroutines              | generic                                     |

| Symbolics                | generic                                     |

| TimeGens                 | tester-specific                             |

| TimePlates               | generic, tester-specific, equation-specific |

| TimingSets               | tester-specific, equation-specific          |

## Generic Program Blocks

This section discusses the specific syntax for each of the generic program blocks. The following list shows the WGL generic program blocks:

|            |             |

|------------|-------------|

| Signals    | TimePlates  |

| Scan Cells | Patterns    |

| Scan State | Subroutines |

| Scan Chain | Symbolics   |

Use the generic program blocks to define objects (such as in TDS WDB) that are not specific to any tester. The generic program blocks are presented in the likely order of use when creating a tester neutral output (such as in WDB).

## Signals

The Signals block is used to declare four types of signal definitions: single-bit signals, multi-bit buses, groups, and multiplexed signals or buses. Groups may include signals, buses, or other groups.

The syntax of the WGL Signals block is:

```

signal

SignalDecl

end

```

A complete BNF syntactical representation of the Signals block follows:

```

Signals ::= "signal" { SignalDecl } "end"

SignalDecl ::= <signalName> [ BusOrGroup ] [ ":" SignalAttributes ] [ Pstate ] ";"

BusOrGroup ::= ( BusRange | GroupMembers | MuxMembers )

BusRange ::= "[" <bitNumber> ".." <bitNumber> "]"

GroupMembers ::= "[" [ SignalReference { "," SignalReference } ] "]"

SignalReference ::= <signalName> [ Range ]

Range ::= "[" <bitNumber> [ ".." <bitNumber> ] "]"

MuxMembers ::= [ MuxPartList ] [ Range ]

MuxPartList ::= "[" <muxPartName> "," <muxPartName> [ { ","

<muxPartName> } ] "]"

SignalAttributes ::= (["mux"] [ Direction ] [FreeRunningClock]) { Strobe } [ Radix ]

[ DutPins ] [ AtePins ]

Direction ::= ( "input" | "output" | "bidir" ) [ ( "reference" | "timing" ) ]

```

```

FreeRunningClock ::= [“freerunningclock”] “period” (Time | <variableName>)

“leadingedge” (Time | <variableName>) “trailingedge” (Time |

<variableName>) “offstate” (“0”|“1”|“D”|“U”)

Strobe ::= ( “in” | “out” ) “when” “[” <validityClause> “]”

Radix ::= “radix” ( “binary” | “octal” | “decimal” | “hex” | “hexadecimal” | “symbolic” )

DutPins ::= “dutpin” “[” DutPinGroup { “,” DutPinGroup } “]”

DutPinGroup ::= ( PinInfo | (” PinInfo { “,” PinInfo } “) ” )

PinInfo ::= PinName| PinNumber

PinName ::= <pinName> [PinNumber]

PinNumber ::= “:” <pinNumber>

AtePins ::= “atepin” “[” AtePinGroup { “,” AtePinGroup } “]”

AtePinGroup ::= ( AtePinInfo | (” AtePinInfo { “,” AtePinInfo } “) ” )

AtePinInfo ::= PinInfo [ “tg” “[” <timeGenName> { “,” <timeGenName> } “]” ]

Pstate ::= “initialp” “[” <TDSstate> “]”

```

The *SignalDecl* begins with a user-defined identifier or string. The *SignalDecl* can be any of four types:

- single-bit signals or multi-bit buses

- groups of signals, buses, or other groups

- multiplexed signals or buses

## Single-Bit Signals

Single-bit signals are defined by an identifier followed by a list of attributes. The following is an example of a WGL Signals block with only single-bit signals defined.

---

Start Example

---

```

signal

clk    : input;

dataReady: output;

in_1   : input;

readWrite: bidir;

```

```

end

```

---

End Example

---

## Buses

Buses are defined by an identifier followed by the range of the bus, enclosed in brackets ( [ ] ). The total, combined number of single-bit signals and buses that can be defined is limited to 16384.

The following is an example of a WGL Signals block with single-bit signals and buses defined.

---

Start Example

---

```

signal

clk: input;  # system clock

dataReady: output;

in_1 : input;

readWrite: bidir;

data [0..31]: bidir; # 32-bit data bus

addr [0..15]: input; # 16-bit address bus

end

```

---

End Example

---

## Groups

Groups are defined by a list of previously defined single-bit signals, buses, bus members, or other groups. Groups can name single-bit signals, buses, bus members, or groups only once in the list. The number of groups used does not contribute to the combined total of 16384.

The following is an example of a WGL Signals block with single-bit signals, buses, and groups defined:

---

Start Example

---

```

signal

clk: input;  # system clock

dataReady: output;

in_1 : input;

readWrite: bidir;

data [0..31]: bidir; # 32-bit data bus

addr [0..15]: input; # 16-bit address bus

busses [data, addr]; # both busses

together data0_8 [data[0..8]];

```

```

oddAddr [addr[1], addr[3], addr[5], addr[7]];

inputs [clk, in];

end

```

---

End Example

---

There are predefined groups available that you can use in any correct syntax for groups. The predefined group names must be entered as upper-case characters, as shown. They are:

### **ALL**

This predefined group contains all signals, buses, and multiplexed signals and buses (but not multiplexed parts). Groups are not included.

### **ALLINPUT**

This predefined group contains all signals, buses, and multiplexed signals and buses (but not multiplexed parts) with the `input` signal direction attribute.

### **ALLOUTPUT**

This predefined group contains all signals, buses, and multiplexed signals and buses (but not multiplexed parts) with the `output` signal direction attribute.

### **ALLBIDIR**

This predefined group contains all signals, buses, and multiplexed signals and buses (but not multiplexed parts) with the `bidir` (bidirectional) signal direction attribute.

### **ALLMUX**

This predefined group contains all multiplexed signals and multiplexed buses (but not multiplexed parts) with the `mux` (multiplexed) signal attribute.

There is no limit to the number of groups that can be defined.

## **Multiplexed Signals or Buses**

Multiplexed signals are defined by an identifier followed by a list of multiplexed parts, enclosed in brackets ( [ ] ); multiplexed buses are defined by an identifier followed by a list of multiplexed parts, enclosed in brackets ( [ ] ), and followed by the *Range*, which is also enclosed within brackets ( [ ] ).

Do not confuse multiplexed parts ( <muxPartName>s ) with signals; multiplexed parts describe the ATE resources used to supply pattern data to a multiplexed signal or bus. Multiplexed parts function in much the same manner as signals in the TimePlates, carrying timing parameters and pattern data that is eventually associated with a multiplexed signal defined in the Signals block.

An example of a WGL Signals block with definitions of a multiplexed signal, a single-bit signal, and a multiplexed bus follows. Note the use of the mux attribute:

---

Start Example

```

Signal

fastClock [edge1, edge2]:mux input;      # Multiplexed parts edge1,

# edge2 on multiplexed

# signal fastClock

rd/_wr      :output;

Databus [bus1, bus2] [0..31]:mux bidir;  # Multiplexed parts bus1,

# bus2 on multiplexed

# bus Databus

end

```

End Example

---

When waveforms are more complicated than those supported by the target tester's formatting set, multiplexed signals and buses are typically used to generate test programs that contain pin multiplexing for these complicated waveforms. By using this ability, you can multiply the effective frequency of the tester. If multiple pattern bits are needed to define a waveform (for example, multiple pulses in a single tester cycle), you should define such signals or buses as multiplexed signals or buses.

Following the optional *BusOrGroup* syntax are other attributes that are associated with the current signal declaration. If you are defining a group, only the radix attribute is applicable.

### **atepin**

ATE pin information is defined in the Signals block using the reserved word atepin. The *AtePinInfo* syntax is used to describe the mapping of the current signal declaration to tester pins and the binding between a tester pin and its timing generators. The atepin value is an alphanumeric string. When multiple ATE pins are specified for a multi-bit bus, the mapping is one-to-one unless parentheses are used to group two or more pin declarations with a single signal.

ATE timing generator information is also defined in the signals block. The timing generator binding is introduced with the reserved word tg. The *tgName* is the name of

the tester-specific timing generator that is generating the timing for all the edges of the signals in the current signal declaration. Multiple *tgNames* indicate that the timing generators are being multiplexed or the existing timing generators (defined in a TimeGens block) are responsible for multiple edges.

## NOTE

---

*Pin information and timing generator information are both tester-specific*

---

The following is an example of a WGL Signals block with dutpin and atepin attributes defined:

---

Start Example

```

Signal

clk : input  dutpin [c:p1] atepin [fclock:123 tg [ACLK1] ];

dr  : input  dutpin [r:p2] atepin [p124:124 tg [BCLK1,

CCLK1] ];

data: output dutpin [d:p3] atepin [p2:2 tg [STRB1]];

end

```

End Example

---

## direction

The direction attribute describes the direction of a signal and controls how the signal is used in test program generation.

A signal may be forcing (input), sensing (output), or both forcing and sensing at different times (bidir); the default is input. A direction may not be specified for groups. If a bus has a direction of input or output, all the bits of the bus must have the same direction; otherwise, only bidir is legal.

To control how the signal is used in test program generation, you can choose either reference or timing. If neither of these is specified, the signal is considered in TimePlate matching and tester program generation. If the clause is used with timing specified, the signal is considered in TimePlate binding but not in test program generation. If reference is specified, the signal is not considered in either TimePlate binding or test program generation. When this clause is used, complete WGL syntax is still required for the signal (signal, TimePlate track, and data).

The following is an example of a WGL Signals block with signals `I1` and `I3` use restricted:

---

Start Example

---

```

signal

I1 : input reference;

I2 : input;

I3 : input timing;

.

.

end

```

---

End Example

---

## freerunningclock

The ‘freerunningclock’ attribute assigns its signal to be a free-running clock with direction being forcing (input), also known as a background clock.

Free-running clocks should be independent from the rest of the signals. They are naturally supported by the testers that have the hardware equivalence which allows free-running clocks to be at any frequency, whether or not in sync with the rest of the signals on the device.

Conversion tools should program these free-running clocks in separate time domain(s) when applicable.

For target testers without multi-time domains or free-running clock support, conversion tools must “condition” them to be able to function in the same time domain as the rest of the signals via alignment or other conditioning techniques.

The keyword “freerunningclock” is case insensitive, and it’s also optional. When a keyword “Period” is seen in the signal attribute along with “LeadingEdge”, “TrailingEdge”, and “OffState”, WGL syntax allows that to be sufficient to define a free-running clock.

The following is an example of two free-running clocks defined in a WGL Signals block, `frc8` and `frc15`:

---

Start Example

---

```

signal

frc8: FreeRunningClock Period 8ns LeadingEdge 2ns TrailingEdge 4ns OffState 0;

frc15:                  Period 15ns LeadingEdge 0ns TrailingEdge 7.5ns OffState U;

end

```

---

End Example

---

The corresponding waveforms for these two example clocks can be expressed in WGL syntax:

```

# For frc8 clock. The intervals from 0ps to 2ns, and 4ns to the end of the

# 8ns period are off states, so they took on 'D' because the specification

# was 'OffState 0'. The 'OnState' from 2ns to 4ns is implied 'U'.

timeplate frc8 period 8ns

Frc8 := input[0pS:D, 2nS:U, 4nS:D];

end

# For frc15 clock. The intervals from 7.5ns to the end of the 15ns period

# is off state, so it took on the state 'U' because the specification was

# 'OffState U'. The 'OnState' from 0ns to 7.5ns is implied 'D'.

timeplate frc15 period 15nS

Frc15 := input[0pS:D, 7.5nS:U];

End

```

## Strobe Clause

Signals and buses may have optional strobe clauses following the direction attribute. Use this clause to specify:

- that an input or output signal is valid only when another signal takes a certain value, or

- the conditions under which a bidirectional signal is an input, and those under which it is an output.

Strobe clauses take the form: **in|out when [ <validityClause> ]**

The <validityClause> takes the form: <signalName> < TDSstate>

The following is an example of a WGL Signals block with strobe clause for signals dr and data:

---

Start Example

```

signal

cntrl      : input;

dr         : bidir in when [cntrl D] out when [cntrl U];

data[7..0]  : output out when [cntrl D];

end

```

---

End Example

---

## dutpin

The dutpin attribute specifies the names (and optional numbers) of the pins on the device-under-test associated with the signal. The dutpin value is an alphanumeric string.

If a device has multiple pins dedicated to the same signal, or different pins in use when a bidirectional signal is input or output, more than one pin may be specified. dutpin may not be specified for groups.

If multiple pins are specified in a multi-bit bus declaration, the mapping is assumed to be one-to-one between the bus elements and the pins, in a left-to-right, most-significant-pin to least-significant-pin order. Other distributions of pins to signals (such as that required for multiplexed pins) can be accomplished by grouping the pin declarations within parentheses.

This indicates that multiple pins are bound to single-bit bus member.

The following is an example of a WGL Signals block with dutpin attribute defined:

---

Start Example

```

signal

clk  : input dutpin [c:1];

data[0..7]: bidir dutpin [

(d0i, d0o), (d1i, d1o), (d2i, d2o),

(d3i, d3o), (d4i, d4o), (d5i, d5o),

(d6i, d6o), (d7i, d7o)];

end

```

End Example

---

## **mux**

The mux attribute defines a signal or bus as a multiplexed signal or bus. The signal or bus receives pattern data from a list of multiplexed parts. If the multiplexed parts are themselves buses, these buses must be followed by the range of the bus enclosed in brackets ( [ ] ).

The names of the multiplexed parts must be identified for the first time in the current signal definition; it is illegal to use the names of other signals, groups, or buses that have been previously defined in the Signals block of the WGL file.

## **initialp**

Each signal definition may have an optional initialp state specified. P states are resolved to this state the first cycle of the waveform. Any legal TDS state may be specified. If the initialp clause is omitted, the default is D (FORCE\_LO). initialp may not be specified for groups.

The following is an example of a WGL Signals block with initialp specified for signals clk and bus:

---

Start Example

```

signal

clk      : input initialp[U];

bus[0..7] : output initialp[X];

end

```

End Example

---

## Radix

The radix attribute describes the base in which the pattern data for the bus is described in the Patterns block. The radix attribute can be binary, hexadecimal, octal, decimal, or symbolic. Only binary and symbolic are legal for single-bit signals. The default radix is binary when the radix attribute is unspecified.

symbolic radix indicates that identifiers defined in subsequent symbolic blocks may be used in pattern vectors. Decimal radix may only be specified for buses and groups with 32 or fewer scalar member signals.

## Scan Cells

The Scan Cells block is used to represent internal storage registers of a device that may be loaded or observed using serial shift scan circuitry. The total number of scan cells allowed in a single WGL In file is limited to 32767.

It is important to distinguish scan cells from signals. Scan cells do not have direction and there is no direct association with ATE or DUT pins. Scan cells cannot be referenced in TimePlates or pattern parameter lists.

The syntax of the WGL Scan Cells block is:

```

scancell

ScanCellDecl

end

```

A complete BNF syntactical representation of the Scan Cells block follows:

```

ScanCells ::= "scancell" { ScanCellDecl } "end"

```

```

ScanCellDecl ::= <cellName> [ ScanGroup ] [ ":" Radix ] ";"

```

```

ScanGroup ::= "[" [ ScanRange | ScanGroupMembers ] "]"

ScanRange ::= <bitNumber> ".." <bitNumber>

ScanGroupMembers ::= CellReference { "," CellReference }

CellReference ::= ( <cellName> [ Range ] )

Range ::= "[" <bitNumber> [ ".." <bitNumber> ] "]"

Radix ::= "radix" ( "binary" | "octal" | "decimal" | "hex" | "hexadecimal" | "symbolic" )

```

The *ScanGroup* statement allows you to specify a logical grouping of scan cells. The scan cells in a group may be from multiple scan chains. Each *ScanGroupMember* must be previously defined, unless it is the name of another scan group.

The optional *Radix* specification for scan groups and registers is used in scan state vectors. The supported radices are implemented by using the WGL reserved words: binary, hex, octal, decimal, and symbolic.

An example of a ScanCells block is:

---

Start Example

```

scancell

latchA;

latchB;

datareg[0..7]: radix hexadecimal;

group_1[latchA, latchB, datareg[7]]: radix octal;

end

```

End Example

---

The Scan Cells block example names scan-able cells within the device. Cells may be single-bit latches, such as `latchA`, or multi-bit registers, such as `datareg`. Logical groups of scan cells, such as `group_1`, also may be specified.

A complete example of WGL scan structures is provided on later on in this document.

## Scan State

Each state declaration in a Scan State block defines the entire state of the set of all scan cells at some instant in time. The goal of input scanning is to achieve that state; the goal of output scanning is to observe that state. A scan state vector may be referenced from

zero or more scan pattern rows. It may take multiple scan chains to load or observe all the cells in a state.

A binary format of the scan vectors is supported (See “[Binary WGL](#)”). This capability allows you to use binary data from a CAE simulation as input to TDS.

The syntax of the WGL Scan State block is:

```

scanstate

ScanStateDecl

end

```

A complete BNF syntactical representation of the Scan State block follows:

```

ScanState ::= "scanState" { ScanStateDecl } "end"

ScanStateDecl ::= <stateName> ":" { StateVectorElement } ;"

StateVectorElement ::= <chainName> "(" { <stateString> } ")"

```

The *ScanStateDecl* specifies a name for the scan state and the values of all the scan cells for that state. The *<stateName>* is an identifier; some special characters may be used if the *<stateName>* is enclosed within double quotation marks ( “ ” ). *<stateNames>* occupy their own name space but must be unique among all other states. The *StateVectorElements* are assigned by naming the cell, register, cell group, or chain and appending a *<stateString>* value in parentheses. The *<stateString>* is interpreted in the radix of the associated cell reference similar to the technique used for pattern states. The WGL Out Converter always generates state vectors using ALLSCAN as the only cell reference. The *<chainName>* is an identifier and must be unique among all other scan chain names.

The value of any cell not specified in the scan state declaration is implicitly X, the TDS state character representing a compare unknown state. The actual value used by a tester to drive X is technology-dependent and programmed in TDS Test Control Language (TCL). If that portion of the state is scanned out, the comparison is masked. For more information on how to use TCL, see the “[Test Control Language](#)” document.

Legal characters in the *stateString* are 0, 1, Z, and X for binary radix, 0-9, A-F, Z, and X for hexadecimal radix, 0-7, Z, and X for octal radix, and 0-9 for decimal radix.

The following is an example of a Scan State block. The bit order of the scan group ALLSCAN is the order that the scan cells (and scan registers) are defined in the Scan Cell block of the WGL file.

---

Start Example

---

```

scanState

state1 := latchA(1) latchB(0)

datareg(3F); state2 := latchA(0)

latchB(1) datareg(01); state3 :=

ALLSCAN(XX00000000); stateX := ;

end

```

---

End Example

---

The `stateX` state declaration in this example sets up a state of all X (compare unknown) values.

A complete example of WGL scan structures is provided later in this document.

## Scan Chain

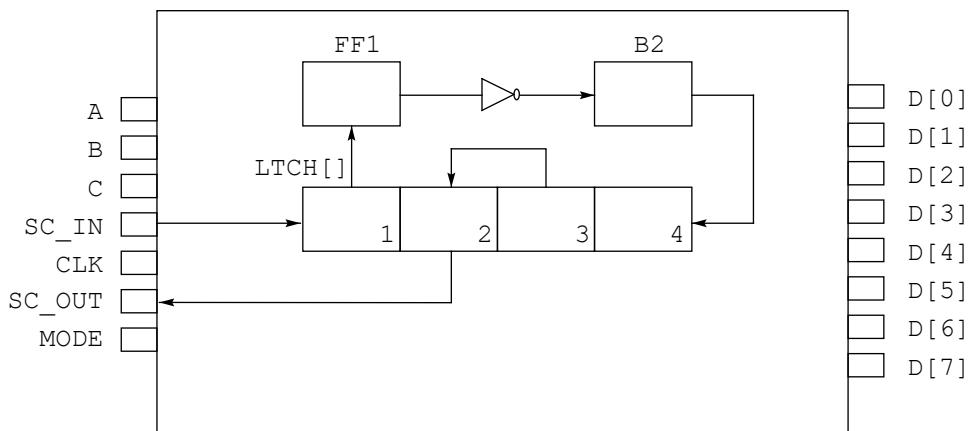

The Scan Chain block defines the configuration of a circuit path connecting edge signals to scan cells and inverters. Each chain is named with an identifier or quoted string that must be unique among signals, scan cells, buses, scan registers, groups, and other scan chains.

The syntax of the WGL Scan Chain block is:

```

scanchain

ChainDecl

end

```

A complete BNF syntactical representation of the Scan Chain block follows:

```

ScanChain ::= "scanChain" { ChainDecl } "end"

ChainDecl ::= <chainName> "[" ChainMembers "]" [ ":" Radix ] ";"

ChainMembers ::= ( OutEdgeSignalOnly | ChainMemList )

OutEdgeSignalOnly ::= "," ChainMemReference

ChainMemList ::= ChainMemReference { "," ChainMemReference }

ChainMemReference ::= ( CellReference | "!" )

CellReference ::= ( <cellName> [ Range ] )

Range ::= "[" <bitNumber> [ ".." <bitNumber> ] "]"

Radix ::= "radix" ( "binary" | "octal" | "decimal" | "hex" | "hexadecimal" | "symbolic" )

```

The <chainName> is an identifier and must be unique among all other scan chain names.

The *ChainMembers* list represents the ordered sequence of scan chain elements where the implied shift direction is left-to-right. When signal names appear in a *ChainMembers* list, the signal names must be the first or last entry in the list.

A signal name appearing at the start of the chain must have been declared input or bidirectional. A signal appearing at the end must have been output or bidirectional. The reserved symbol ! indicates state inversion. Scan chains may be members of other chains as long as the declaration is not recursive.

Either the input edge signal or the output edge signal can be omitted, but if the chain is directly referenced by a scan pattern row, at least one must be present.

If the *Radix* is omitted, binary radix is supplied by default.

An example of a Scan Chain block is:

---

Start Example

```

Scanchain

chain1 [ SC1_IN, datareg[0], latchA, datareg[2], SC1_OUT] : radix

octal; chain2 [ SC2_IN, datareg[1], !, datareg[7], datareg[5], latchB,

datareg[4], !, datareg[6]];

end

```

End Example

---

The Scan Chain block example shows the order of scan cells on two physical chains. The first and last elements of the `chain1` cell list are the names of edge signals `SC1_IN` and `SC1_OUT`, which must have been defined previously in a Signals block. `chain2` has an input signal `SC2_IN` but no corresponding output signal. Therefore, `chain2` may be used to control the state of the listed scan cells but there is no way to observe their state. The reserved symbol ! appears twice in the `chain2` cell list. This indicates that states are inverted when they shift between `datareg[1]` and `datareg[7]`, and between `datareg[4]` and `datareg[6]`.

Parallel scan chains are supported, but the scan chains can not be identical. The following is an example of the legal use of parallel scan chains.

---

Start Example

```

waveform t1

scancell

```

---

```

latch1; latch2; latch3; latch4; latch5; latch6; latch7; latch8;

end

scanstate

state1 := latch1(0) latch2(0) latch3(0) latch4(0);

state2 := latch1(0) latch2(0) latch3(0) latch4(1);

state3 := latch1(0) latch2(0) latch3(1) latch4(1);

state4 := latch1(0) latch2(1) latch3(0) latch4(0);

state5 := latch1(0) latch2(1) latch3(0) latch4(1);

estate1 := latch5(1) latch6(1) latch7(1) latch8(0);

estate2 := latch5(1) latch6(1) latch7(0) latch8(1);

estate3 := latch5(1) latch6(1) latch7(0) latch8(0);

estate4 := latch5(1) latch6(0) latch7(1) latch8(1);

estate5 := latch5(1) latch6(0) latch7(1) latch8(0);

estateX := ;

end

signal

clock : input;

scanIO : bidir;

scanOut :

output; enable :

input;

end

scanChain

chain1 [scanIO, latch1, latch2, latch3, latch4];

chain3 [latch1, latch2, latch3, latch4, scanIO];

chain2 [latch5, latch6, latch7, latch8, scanOut];

end

timeplate scanTiming period 200ns

clock := input [0ps:D, 50ns:S, 100ns:D];

enable := input [0ps:S];

scanIO := input [0ps:S];

scanIO := output [0ps:X, 50ns:Q];

scanOut := output [0ps:X, 50ns:Q,

90ns:X]; end

pattern pat1 (clock, enable, scanIO:I, scanIO:O, scanOut)

vector(+, scanTiming):=[1 1 1 - X];

scan(+, scanTiming):=[1 1 - - -], input[chain1:state1],

output[chain3:estate1];

vector(+, scanTiming):=[1 1 1 - X];

scan(+, scanTiming):=[1 1 - - -], input[chain1:state2],

output[chain2:estate2];

vector(+, scanTiming):=[1 1 1 - X];

scan(+, scanTiming):=[1 1 - - -], input[chain1:state3],

```

```

output[chain2:estate3];

vector(+, scanTiming):=[1 1 1 - X];

scan(+, scanTiming):=[1 1 - - -], input[chain1:state4],

output[chain2:estate4];

vector(+, scanTiming):=[1 1 1 - X];

scan(+, scanTiming):=[1 1 - - -], input[chain1:state5],

output[chain2:estate5];

end

end

```

---

End Example

---

A complete example of WGL scan structures is provided later in this document.

## TimePlates

The TimePlates block is used to define the timing component of the waveforms. The TimePlates convey the unique kinds of timing that are present in the overall waveforms.

The syntax of the WGL TimePlate block is:

**timeplate** <timeplateName> *TimePlate* **end**

A complete BNF syntactical representation of the TimePlates block follows:

```

Timeplates ::= "timeplate" <timeplateName> TimePlate "end"

TimePlate ::= "period" TimeReference [ "timeset" <tsNumber> ] Channels

TimeReference ::= (Time | <variableName>)

Time ::= <timeValue> Unit

Unit ::= ( "ps" | "ns" | "us" | "ms" | "sec" )

Channels ::= { SignalReference { "," SignalReference } ":" Track }

SignalReference ::= <signalName> [ Range ]

Range ::= "[" <bitNumber> [ ".." <bitNumber> ] "]"

Track ::= [ Direction ] [ "[" FirstEvent { "," Event } "]" ] ";"

Direction ::= ( "input" | "output" | "bidir" ) [ ( "reference" | "timing" ) ]

FirstEvent ::= "0" Unit ":" <TDSstate> [ " " ( "edge" | "window" ) ]

```

Event ::= TimeReference ":" <TDSstate> [ " " ( "edge" | "window" ) ]

<timeplateName> is an identifier used to reference the TimePlate throughout later portions of the WGL program. An overall timing period is assigned to each TimePlate by the reserved word period. The *TimePlate* declaration is a definition of the constituent parts of the TimePlate.

<variableName> is the name of a variable that has been previously defined in the ExprSet sub-block of an EquationSheet block. (See "[ExprSet](#)" later in this document.)

Each TimePlate is given an overall time period applying to the length of the cycle following the reserved word period. The period can be a numeric value greater than zero, or a variable having been previously defined in the ExprSet sub-block of an EquationSheet block.

### **NOTE**

---

*A variable used in the TimePlates block must have a value that is meaningful when expressed in units of time.*

---

A TimePlate contains a list of signal *Channels*. Each *Channel* can contain one or more signals, buses, groups, or multiplexed parts. These entities must have been previously declared in the Signals block. Each *Channel* associates the signals with a *Track*. Conceptually, a *Channel* is a container for one or more signal names, each of which is followed by a *Track*. The *Track* itself contains the actual information about the shape and timing of the waveform, and its *Direction*. The *TDSstates* that are used must be consistent with those available for the direction of input or output. (See [Table 7](#) for a list of TDS state characters.) All the signals that share the channel must also have a compatible direction.

### **NOTE**

---

*It is important to note that while multiplexed parts are permitted, multiplexed signals or buses (those signals or buses tagged with the **mux** attribute in the Signals block that receive their timing parameters from multiplexed parts) are not permitted. In effect, timing is defined for the multiplexed parts, which then supply data for the multiplexed signal or bus with which they are associated in the Signals block.*

---

The first event in a *Track* must have a literal time value of 0. Timing supplied by a variable is not legal for the first event. Subsequent events can use either a literal time value or a variable to specify the timing of the event. A variable, if used, must have been previously defined in the *ExprSet* sub-block of an *EquationSheet* block.

The reserved word *timeset* lets you define a tester-specific timing set name that is associated with the timing in the *TimePlate*. The following is an example of a simple *TimePlates* block:

---

Start Example

```

timeplate read period 250ns timeset 1

clock := input [0ps:D, 50ns:U, 100ns:D, 150ns:U, 200ns:D,

250ns:U];

in   := input [0ps:D,170ns:U];

out  := output [0ps:X,180ns:Q'edge, 220ns:X];

end

```

End Example

---

A bidirectional signal can occupy one channel if the direction is specified using the reserved word *bidir*, or two channels if the direction is defined using both of the reserved words *input* and *output*. In the first instance, the channel is doing intra-cycle input/output switching; in the second instance, the channel is doing inter-cycle input/output switching. These two can be combined to make a maximum of three channels per signal.

Contained within each *Track* is a comma-separated list of events. Each event consists of a time value defined by *Time* and a *TDSstate*. For input channels, the TDS force logic state characters must be used; for output channels, TDS expect logic state characters must be used; for bidirectional channels, both force and expect TDS state characters may be used. The TDS state character S indicates that the actual state character is to be “substituted” into the waveform at that point. The actual state character comes from the data bit in the corresponding column in a pattern block. In other words, when *Track* contains an S state character, the actual state is derived from the pattern data. The TDS state character P indicates that the state is to be provided from the previous state (from the previously juxtaposed template). The TDS state character C indicates that the state is the complement of the substituted state. See [Table 7](#) for a list of TDS logic state characters.

For output channels, the compare logic states must be used. The TDS state character Q indicates that the state is to be substituted from the data bit from the corresponding column in a pattern block. The TDS state character R indicates that the state is the

complement of the substituted state. The optional reserved words edge or window (default) can follow an output state to indicate edge or window strobing to be produced in the target tester strobe format.

An example of a typical TimePlates block, including the corresponding signal definitions in the Signals block and the pattern data defined in the Patterns block, follows. (Note the use of multiplexed buses.)

---

Start Example

---

```

signal

=====

# FastClock is generated using eight multiplexed components.

# Databus bus is made up of two separate busses, bus1 and bus2.

=====

FastClock[edge0, edge1, edge2, edge3, edge4, edge5, edge6, edge7]: mux input;

rd/_wr                      : output;

Databus[bus1, bus2][0..3]    : mux bidir; # Multiplexed the two four bit

# busses to get a byte-wide bus.

end

timeplate writeTP period 80ns

edge0: input[0ps:D, 2ns:U, 8ns:D, 10ns:?]; # Clock for data bit bus1[0]

edge1: input[0ps:?, 10ns:D, 12ns:U, 18ns:D, 20ns:?]; # Clock for data bit bus1[1]

edge2: input[0ps:?, 20ns:D, 22ns:U, 28ns:D, 30ns:?]; # Clock for data bit bus1[2]

edge3: input[0ps:?, 30ns:D, 32ns:U, 38ns:D, 40ns:?]; # Clock for data bit bus1[3]

edge4: input[0ps:?, 40ns:D, 42ns:U, 48ns:D, 50ns:?]; # Clock for data bit bus2[0]

edge5: input[0ps:?, 50ns:D, 52ns:U, 58ns:D, 60ns:?]; # Clock for data bit bus2[1]

edge6: input[0ps:?, 60ns:D, 62ns:U, 68ns:D, 70ns:?]; # Clock for data bit bus2[2]

edge7: input[0ps:?, 70ns:D, 72ns:U, 78ns:D, 80ns:?]; # Clock for data bit bus2[3]

rd/_wr: input[0ps:?, 20ns:D, 80ns:?];      # Indicate write cycle

bus1[0]: input[0ps:D, 5ns:S, 10ns:?];      # Data bit 0

bus1[1]: input[0ps:?, 10ns:D, 15ns:S, 20ns:?];# Data bit 1

bus1[2]: input[0ps:?, 20ns:D, 25ns:S, 30ns:?];# Data bit 2

bus1[3]: input[0ps:?, 30ns:D, 35ns:S, 40ns:?];# Data bit 3

bus2[0]: input[0ps:?, 40ns:D, 45ns:S, 50ns:?]; # Data bit 4

bus2[1]: input[0ps:?, 50ns:D, 55ns:S, 60ns:?]; # Data bit 5

bus2[2]: input[0ps:?, 60ns:D, 65ns:S, 70ns:?]; # Data bit 6

bus2[3]: input[0ps:?, 70ns:D, 75ns:S, 80ns:?]; # Data bit 7

end

pattern load1( FastClock, rd/_wr, Databus)

vector(+, writeTP) := (11111111 1 10101010XXXXXXXX);

end

```

---

End Example

---

You can see in the example that the multiplexed parts do not need be defined as contiguous sections of the timing track; gaps in the defined timing for the multiplexed parts are allowed to support the requirements of your particular tester.

The multiplexed parts can occur in any order in the TimePlate block, as can the timing defined in the timing track. For example, the timing for *edge7* and *edge2* could legally be defined as:

```

edge2: input[0ps:?, 70ns:D, 72ns:U, 78ns:D, 80ns:?] ;

. . .

edge7: input[0ps:?, 20ns:D, 22ns:U, 28ns:D, 30ns:?] ;

```

As you can see, the timing values are in the reverse order of those shown in the example.

The pattern data (11111111 1 10101010XXXXXXXX) is mapped to the buses and signals as described in “Patterns” later in this document.

An edge strobe is an instruction to the tester comparator hardware to take an instantaneous sample of the DUT output, and compare it with the expect data. A window strobe tells the tester comparator hardware to verify that the expect data is appearing at the DUT throughout a window of time. If neither reserved word is specified, the event is assumed to be a window strobe.

When defining a track, make sure that you assign increasing time values for each event subsequently defined, whether using a constant time value or a variable; the first event of the waveform must always begin at 0pS, and it is unacceptable to define a second event at 20nS and a third event at 15nS. Remember that all event times are relative to the beginning of the cycle.

TimePlates used with scan pattern rows must satisfy certain requirements. Those signals that terminate scan chains referenced from the same pattern row must have sample states; that is, signals that appear at the start of a scan chain must have an S state character, and signals that appear at the end of a scan chain must have a Q state character in their respective waveform shapes. Any other state characters will be a violation.

The following is an example of a TimePlates block that can be used with scan pattern rows:

---

Start Example

---

```

timeplate runSC period 500ns

SC1_IN := input[0pS:S, 250nS:D];

SC2_IN := input[0pS:S, 250nS:D];

SC1_OUT := output[0pS:X, 250nS:Q];

```

```

SC_CLOCK := input[0pS:U, 250nS:D];

SC_EN := input[0pS:U];

BUS_D := output[0pS:X];

ADDR_IN := input[0pS:P];

end

```

---

End Example

---

## NOTE

---

*In the above example, only signals containing TDS state characters for unresolved states (such as S or Q) are scan signals (signals that terminate scan chains).*

---

You can use variables in the place of literal time values in the TimePlates block. The variables must be previously defined in a default ExprSet sub-block of an EquationSheet block. (See “[ExprSet](#)” later in this document.)

Variables can be substituted for the TimePlate period value and any event time. You can intermix literal time values and variables, although the initial event in a time track must occur at 0pS, and it must be expressed as a literal time value.

The following example shows how variables that were defined in an EquationSheet block can be used in a TimePlate block. The use of variables is highlighted in **bold** typeface:

---

Start Example

```

timeplate ts1 period write_cycle

clk := input[0pS:D, 20nS:U, tclk1:D, 90nS:U];

ale := input[0pS:D, t1:S, t2:D];

RE := input[0pS:D, 20nS:S, 50nS:D];

OE := input[0pS:P, 30nS:S];

strobe := output[0pS:X, t3:Q, 90nS:X];

end

```

---

End Example

---

## Patterns

The Patterns block is used to define rows of data bits. These rows are also called vectors. The vectors defined in the Patterns block are to be modulated through the TimePlate that is associated with each vector. The result of this modulation creates the waveform.

A binary format of the pattern vectors, to be used in place of ASCII pattern data, is supported. See “[Binary WGL](#)” section later in this document. This capability allows you to use binary pattern data from a CAE simulation as input to TDS. You cannot mix ASCII pattern vectors and binary pattern data within a Pattern block. However, you can have an ASCII Pattern block and a binary Pattern block within a WGL file.

The syntax of the WGL Patterns block is:

```

pattern <patternName>

PatternParameters PatternRows

end

```

A complete BNF syntactical representation of the Patterns block follows:

```

Patterns ::= "pattern" PattName "(" PatternParameters ")"

PatternRows "end"

PattName ::= ( <patternName> | <patternNameStr> )

PatternParameters ::= PatternParam { ";" PatternParam }

PatternParam ::= SignalReference [ ":" ( "I" | "O" ) ]

SignalReference ::= <signalName> [ Range ]

Range ::= "[" <bitNumber> [ ".." <bitNumber> ] "]"

PatternRows ::= { [ <vectorLabel> ":" ] ( Loop | Repeat | ScanRow ) }

Loop ::= "loop" [ <loopName> ] <loopCount>

PatternRows "end" [ <loopName> ]

Repeat ::= [ "repeat" <repeatCount> ] ( Vector | Call | Offset )

Vector ::= "vector" Address ":" PatternExpression [ TimeComment ] ";"

Address ::= "(" AddressElement { ";" AddressElement } ")"

AddressElement ::= ( "+" | <cycleNumber> | [ Time ] | <timeplateName> ) Time ::=

<timeValue> Unit

Unit ::= ( "ps" | "ns" | "us" | "ms" | "sec" )

PatternExpression ::= "[" { ( <stateString> | <patternIdentifier> ) } "]"

```

```

TimeComment ::= "(" Time ")"

Call ::= "call" <subroutineName> "(" ";" ;

Offset ::= "skip" Time ";" ;

ScanRow ::= "scan" Address ":" ScanRowElement { "," ScanRowElement } ";" ;

ScanRowElement ::= (PatternExpression | ScanRun)

ScanRun ::= ScanDir "[" <chainName> ":" <stateName> "]"

ScanDir ::= ( "input" | "output" | "feedback" )

```

Multiple Pattern blocks are allowed in WGL and are used to describe a way of partitioning a test program into pattern bursts in the target tester.

<patternName> is a user-defined name such as `Group_ALL`.

<patternNameStr> is a user-defined name such as `"Group+two"`. (String notation allows the use of characters not otherwise permitted.) The <patternName> and <patternNameStr> user-defined names are stored in the TDS WDB. Third party tools should also store them or pass them through to the target tester program.

The *PatternExpression* defined for each identifier must contain legal pattern <stateString>s. The number of bits in the *PatternExpression* must be the same as the number of bits in the corresponding signal, bus, group, or multiplexed signal or bus that is associated with it.

*PatternParameters* is a parentheses-enclosed list of signal names that have already been defined in the Signals block. The *PatternParameters* are used to map signals, buses, groups, and multiplexed signals or buses (defined in the Signals block) to columns in the *PatternExpressions*. If multiplexing is used for signals or buses, the pattern bits are combined under the control of the associated radix, in exactly the same manner that the pattern bits are controlled for non-multiplexed buses. For multiplexed parts, the binding order of the pattern bits is left-to-right as specified in the multiplexed signal definition in the Signals block. Each *PatternParam* in the parameter list corresponds in order of occurrence to columns of data in each vector statement.

Each column should have a <stateString> bit delimited by a space. For a column with a multi-bit signal (buses, groups, multiplexed), there should be <stateString> bits without space delimiters. The number of bits are as specified in the Signals block. For instance, if a group is specified to have 3 signal members, then the number of <stateString> bits would be 3, and the <stateString> bits should not have spaces between each two bits (for

instance, 000, 101, 111, etc). This convention applies to groups, buses, and multiplexed signals.

For example, if one of the identifiers in the *PatternParameters* has a group, *clocks*, in the column, the <stateString> bits of *clocks* should not have spaces between bits to represent one column, *clocks*.

```

signal

sig1 : input;

c1 : input;

c2 : input;

c3 : input;

clocks [c1, c2, c3];

timeplate ts1 period 10ns

sig1 := input[0pS:P, 5nS:S];

clocks := input[0pS:D, 5nS:U];

end

pattern group_ALL (sig1, clocks)

vector(0, ts1) := [0 111];

vector(1, ts1) := [1 000];

vector(2, ts1) := [0 101];

end

```

*PatternRows* are definitions of rows of data bits used to supply data to waveforms when modulated through a TimePlate, as defined in the TimePlate block.

The optional *TimeComment* provides a mechanism for binding a time to a *Vector*. It is stored in the database as a comment only.

A *Vector* consists of an *Address* and an associated pattern expression. The simplest form of an *Address* is an integer cycle number. A plus sign ( + ) can be used as an address to automatically increment the cycle number from the previous row. The starting time of the cycle may also appear in the address. If a <timeplateName> is mentioned in an *Address*, it must reference an existing TimePlate.

The <patternIdentifier> can be used in subroutines, pattern blocks, or scan state vectors as a shorthand for *PatternExpression* when the radix of the associated signal, bus, group, or scan element is set using the reserved word *symbolic*. See the [Symbolics](#) section in this chapter for more information on how to use the reserved word *symbolic*.

The following vector declaration uses an integer address ( 0 ), starting time of the cycle ( 0pS ), the TimePlate name with which the vector is associated ( t1 ), and the pattern data ( [ 1 ZZZZZZZZ ] ).

```

vector(0, 0pS, t1) := [ 1 ZZZZZZZZ ];

```

The vector declaration below uses only automatic increment address ( + ) and the pattern data ( [1- 111111100000000 1 -] ).

```

vector(+) := [1- 111111100000000 1 -];

```

Vectors and subroutine calls may have optional repeat counts. To cause the vector to be used more than once, the reserved word repeat and a repeat count are used.

The following is an example of a simple WGL Patterns block:

---

Start Example

```

pattern group_ALL (C0,C1,C2,C3,C4,C5,C6,C7,C8)

vector(0, TimeSet0_0) := [0 0 0 1 1 0 1 1 0 ];

vector(1, TimeSet1_0) := [1 1 1 0 0 1 1 1 1 ];

vector(2, TimeSet1_1) := [0 1 1 0 1 1 0 1 0 ];

vector(3, TimeSet2_0) := [1 1 1 1 1 1 0 1 1 ];

vector(4, TimeSet3_0) := [0 0 0 0 0 0 1 1 1 ];

vector(5, TimeSet3_1) := [0 0 0 0 1 0 1 0 0 ];

end

```

---

End Example

---

The example below is a WGL Patterns block with a repeat statement that describes a waveform which has a periodic clock for two cycles and an 8-bit data bus that has a value of all Hi-Z for the first cycle, and a value of 0001 1010 for the second cycle. The repeat statement causes third through sixth cycles of the waveform to all have the same value on the data bus.

---

Start Example

```

signal

clock      : input;

data[0..31] : input radix binary;

end

timeplate t1 period 200ns

clock := input[0ps:D, 100ns:S, 150ns:D];

```

---

```

data  := input[0ps:Z, 120ns:S] radix binary;

end

pattern load1 (clock, data[8..15])

vector(0, 0ps, t1) := [ 1 ZZZZZZZZ ] (100ns);

vector(1, 200ns, t1) := [ 1 00011010 ] (300ns);

repeat 4 vector(3, 200ns, t1) := [ 1 00011010 ];

end

```

---

End Example

---

Bidirectional *patternParameters* always require twice the number of pattern columns to account for input and output directions. If a bidirectional single-bit signal is mentioned as a pattern parameter, two adjacent bits are required (no space between them is allowed). If a bidirectional signal is mentioned with an :I or :O, this counts as one parameter per occurrence. A space is required between them if both directions are used. Bidirectional buses have all of their input pattern bits mentioned first, followed by the output pattern bits. If an :I or :O is used on a bidirectional bus, this counts as one pattern parameter, and at least one space is required as a separator.

The number of bits for each pattern parameter must be the same as the width of the signal, bus, group, or multiplexed signal or bus. The number of bits for a bus is the difference between its upper and lower bounds, plus one. The number of bits in a group is the sum of the number of bits of all the group members. The number of bits for a single direction multiplexed bus is the width of the bus times the number of multiplexed parts. The number of bits for a bidirectional multiplexed bus is the width of the bus times the number of the multiplexed parts times two.

The following is an example of a WGL Patterns block with bidirectional bus pattern spacing:

---

Start Example

```

signal

foo[0..7] : bidir radix binary;

fee[0..7] : bidir radix

hexadecimal; fum[0..7] : bidir

radix hexadecimal; end

pattern load1 (foo,fee,fum:I,fum:O)

vector(+) := [10101010----- FF-- F- -

-];

```

---

End Example

---

The `:I` and `:O` can only be used with bidirectional signals, buses, groups, multiplexed signals or buses, or parts of multiplexed signals or buses.

If the number of the pattern bits in the vector statement does not equal the sum of the bits assigned to the buses defined in the Signals block (that is, the bus range, see “[Buses](#)”), an error is reported.

The reserved word `call` invokes a pattern subroutine, as indicated by the `<subroutineName>`. The rows of the subroutine are treated exactly as if they had been included in-line at the point of the call. Like vectors, calls may have optional repeat counts specified.

The following is an example of a WGL Patterns block with subroutine call `foo`:

---

Start Example

```

pattern load1 (clock, data[8..15])

vector(0, 0ps, t1) := [ 1 ZZZZZZZZ ];

call foo();

vector(+, t1) := [ 1 00011010 ];

end

subroutine foo() vector(t1) :=

[ 1 00011111 ];

end

```

End Example

---

The reserved word `loop` allows a sequence of other vectors, calls, and loops to be repeated a specified number of times. Loops can be nested to any depth. Loops have optional names that have no significance other than as a commentary tag.

The following is an example of a WGL Patterns block with loop `loopName`:

---

Start Example

```

pattern load1 (clock, data[8..15])

vector(0, 0ps, t1) := [ 1 ZZZZZZZZ ];

loop loopName 3 call foo();

vector(+, t1) := [ 1 00011010 ];

end loopName end

```

End Example

---

The reserved word `skip` provides for the declaration of a time period when the waveform state is unspecified. Signal states and event timing are suppressed during the skipped period. The following is an example of a WGL Patterns block with a skip of 400nS:

---

Start Example

---

```

pattern load1 (clock, data[8..15])

vector(0, 0pS, t1) := [ 1 ZZZZZZZZ ];

vector(+, t1)      := [ 1 00011010 ];

skip 400nS;

vector(+, 0pS, t1) := [ 1 ZZZZZZZZ ];

vector(+, t1)      := [ 1 00011010 ];

end

```

---

End Example

---

Scan pattern rows may appear in pattern blocks freely intermixed with the other row types. Each row represents an arbitrary number of cycles dependent on the lengths of the scan chains that it references.

Note that the scan state defines the values of all scan cells in the device. Only those scan cells on the indicated scan chain(s) are loaded or observed by a particular scan row. Other scan cells not referenced by a chain in the pattern row are not affected by the row. Multiple combinations of chain, state, and direction may appear in each scan row. This provides for parallel scan chains or simultaneous loading and observing of a single chain. It is illegal, however, for a scan row to specify the same chain more than once if the direction of the chain is the same but state values associated with the chain are different.

The following is an example of parallel scan chains:

---

Start Example

---

```

pattern pat1 (clock, enable, scanIn, scanOut, scanIn1, scanOut1)

vector(+, scanTiming) := [1 1 1 1 1 1];

scan(+, scanTiming)  := [1 1 - - - -],

input[chain1:state1],

output[chain2:estate1],

input[chain11:state3],

output[chain12:estate3] ;

vector(+, scanTiming) := [1 1 1 1 1 1];

vector(+, scanTiming) := [1 1 1 1 1 1];

end

```

---

End Example

---

It is illegal for a scan chain with no input edge signal to follow the reserved word input. It is illegal for a scan chain with no output edge signal to follow the reserved word output.

The reserved word feedback indicates that the signals appearing on the chain output should be directed back into the chain input while simultaneously comparing against the specified scan state vector. Chains referenced in a feedback clause must have both an input and an output signal. For more information, see “[Scan Chain](#)”.

It is important to make certain that signals that terminate scan chains have the proper state character supplied to them, either from parallel pattern data or from the scan chain associated with the scan run. The following example illustrates a common error made in using scan chains.

---

#### Start Example

---

```

waveform t1

scancell

latch1; latch2; latch3; latch4;    latch5;

latch6; latch7; latch8;

end

scanstate

state1 := latch1(0) latch2(0) latch3(0) latch4(0);

state2 := latch1(0) latch2(0) latch3(0) latch4(1);

.

.

estate1 := latch5(1) latch6(1) latch7(1) latch8(0); estate2 :=

latch5(1) latch6(1) latch7(0) latch8(1); estate3 := latch5(1)

latch6(1) latch7(0) latch8(0);

.

end

signal

clock : input;

scanIO : bidir;

scanOut : output;

enable : input;

end

scanChain

chain1 [scanIO, latch1, latch2, latch3, latch4];

chain3 [latch1, latch2, latch3, latch4, scanIO];

chain2 [latch5, latch6, latch7, latch8, scanOut];

```

```

end

timeplate scanTiming period 200ns

clock := input [0ps:D, 50ns:S, 100ns:D];

enable := input [0ps:S];

scanIO := input [0ps:S];

scanIO := output [0ps:X, 50ns:Q];

scanOut := output [0ps:X, 50ns:Q, 90ns:X];

end

pattern pat1 (clock, enable, scanIO:I, scanIO:O, scanOut)

vector(+, scanTiming) :=[1 1 1 - X];

scan(+,scanTiming)      :=[1 1 - - -], input[chain1:state1],

output[chain3:estate1];

. . .

end

end

```

---

End Example

---